cu metallization process in ic wafer fabrication This technology is based on a selective chemical modification (SCM) of field areas of a wafer or substrate and can be implemented for either a fill-based integration, such as Cu . These horizontal machining centers are designed for cutting hard-to-cut metal and heavy-duty milling. These machines are equipped with a heavy duty, gear-driven spindle that is optimal for shops in power generation, defense, light rail, aerospace and more.

0 · semiconductor copper wafers

1 · metallization semiconductor process

2 · metallization process pdf

3 · metallization hong kong pdf

4 · conductive film metallization

5 · cmp semiconductor wafers

6 · aluminum and copper metallization pdf

7 · advanced metallization and processing pdf

Bridgeport Series I cnc milling machines for sale. Find used vertical milling machines and horizontal milling machines on Machinio.

The process flow of Cu dual damascene metallization is described as below: After processing of Metal-1 (M-1), the etching stop layer (Cu barrier dielectric layer) and the Via-1 (V-1)/Metal-2 (M-2) dielectric layer (e.g., SiCOH .Figure 10.1 depicts the metallization scheme of a MOSFET. The primary metallization applications can be divided into three categories: gate, contact, and interconnection. Polysilicon and silicide .part i: metallization - overview, concerns, and advanced technology •manufacturing and technology requirements for submicron multilevel metal 3 t.e. seidel •self-aligned, metal . This technology is based on a selective chemical modification (SCM) of field areas of a wafer or substrate and can be implemented for either a fill-based integration, such as Cu .

Metallization based on ED has been a practical method for a long time for Cu interconnect metallization of IC chips. It is a time- and cost-efficient process that can fill the high-aspect .

The dual Damascene process for Cu chip metallization and the C4 (flip-chip) technology for area array chip-package interconnection have placed electrochemical . Copper (Cu) has been applied in sub 130 nm semiconductor metallization processes because of its low resistivity and better reliability. As the semiconductor electronics industry .Abstract— Copper metallization in Integrated Circuit interconnect, poses big challenges in Semiconductor Wafer processing. In addition to the stringent Dual Damascene requirement, .

Fabrication of arrays of (100) Cu under-bump-metallization for 3D IC packaging Abstract: Due to the thousands of microbumps on a chip for 3D ICs, the precise control of the microstructure of .

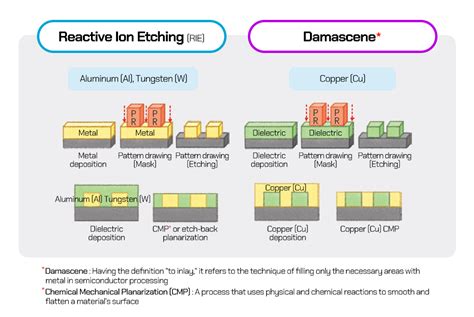

The process flow of Cu dual damascene metallization is described as below: After processing of Metal-1 (M-1), the etching stop layer (Cu barrier dielectric layer) and the Via-1 (V-1)/Metal-2 (M-2) dielectric layer (e.g., SiCOH low-k) are subsequently deposited. In this final episode of our series on front-end processes, we will introduce the process of metallization which connects semiconductor devices using metals such as aluminum and copper. As these interconnections provide power and enable the chip’s operation, they highlight the significance of metallization in semiconductor manufacturing.Figure 10.1 depicts the metallization scheme of a MOSFET. The primary metallization applications can be divided into three categories: gate, contact, and interconnection. Polysilicon and silicide are frequently used in gates and interconnects in MOS devices.part i: metallization - overview, concerns, and advanced technology •manufacturing and technology requirements for submicron multilevel metal 3 t.e. seidel •self-aligned, metal-masked dry etch processing of iii-v electronic and photonic devices 19 s.j. pearton, a. katz, a. feingold, f. ren, t.r. fullowan, j.r. lothian, and c.r. abernathy

This technology is based on a selective chemical modification (SCM) of field areas of a wafer or substrate and can be implemented for either a fill-based integration, such as Cu dual damascene, or an additive process such as plating of wide conductive lines.Metallization based on ED has been a practical method for a long time for Cu interconnect metallization of IC chips. It is a time- and cost-efficient process that can fill the high-aspect-ratio trenches without voids and seams. The dual Damascene process for Cu chip metallization and the C4 (flip-chip) technology for area array chip-package interconnection have placed electrochemical technologies among the most sophisticated fab processing technologies. Copper (Cu) has been applied in sub 130 nm semiconductor metallization processes because of its low resistivity and better reliability. As the semiconductor electronics industry continues its efforts in miniaturizing the integrated circuit (IC), an IC chip with copper interconnect back end of line (BEOL) structures has been developed for .

Abstract— Copper metallization in Integrated Circuit interconnect, poses big challenges in Semiconductor Wafer processing. In addition to the stringent Dual Damascene requirement, the Cu material itself is prone to rapid interface diffusion as well as surface oxidation.

semiconductor copper wafers

metallization semiconductor process

Fabrication of arrays of (100) Cu under-bump-metallization for 3D IC packaging Abstract: Due to the thousands of microbumps on a chip for 3D ICs, the precise control of the microstructure of all the material is required.

The process flow of Cu dual damascene metallization is described as below: After processing of Metal-1 (M-1), the etching stop layer (Cu barrier dielectric layer) and the Via-1 (V-1)/Metal-2 (M-2) dielectric layer (e.g., SiCOH low-k) are subsequently deposited.

In this final episode of our series on front-end processes, we will introduce the process of metallization which connects semiconductor devices using metals such as aluminum and copper. As these interconnections provide power and enable the chip’s operation, they highlight the significance of metallization in semiconductor manufacturing.

Figure 10.1 depicts the metallization scheme of a MOSFET. The primary metallization applications can be divided into three categories: gate, contact, and interconnection. Polysilicon and silicide are frequently used in gates and interconnects in MOS devices.

part i: metallization - overview, concerns, and advanced technology •manufacturing and technology requirements for submicron multilevel metal 3 t.e. seidel •self-aligned, metal-masked dry etch processing of iii-v electronic and photonic devices 19 s.j. pearton, a. katz, a. feingold, f. ren, t.r. fullowan, j.r. lothian, and c.r. abernathy This technology is based on a selective chemical modification (SCM) of field areas of a wafer or substrate and can be implemented for either a fill-based integration, such as Cu dual damascene, or an additive process such as plating of wide conductive lines.Metallization based on ED has been a practical method for a long time for Cu interconnect metallization of IC chips. It is a time- and cost-efficient process that can fill the high-aspect-ratio trenches without voids and seams. The dual Damascene process for Cu chip metallization and the C4 (flip-chip) technology for area array chip-package interconnection have placed electrochemical technologies among the most sophisticated fab processing technologies.

Copper (Cu) has been applied in sub 130 nm semiconductor metallization processes because of its low resistivity and better reliability. As the semiconductor electronics industry continues its efforts in miniaturizing the integrated circuit (IC), an IC chip with copper interconnect back end of line (BEOL) structures has been developed for .Abstract— Copper metallization in Integrated Circuit interconnect, poses big challenges in Semiconductor Wafer processing. In addition to the stringent Dual Damascene requirement, the Cu material itself is prone to rapid interface diffusion as well as surface oxidation.

metallization process pdf

metallization hong kong pdf

Discover Company Info on US METAL FABRICATORS, INC. in Dania Beach, FL, such as Contacts, Addresses, Reviews, and Registered Agent.

cu metallization process in ic wafer fabrication|metallization semiconductor process